Stuart Clubb

Stuart is responsible for Catapult HLS Synthesis and Verification Solutions since July 2017. Prior to this new role, Stuart had been successfully managing the North American FAE team for Mentor/Siemens and Calypto Design Systems and was key to the growth achieved for the CSD products after the Calypto acquisition. Moving from the UK in 2001 to work at Mentor Graphics, Stuart held the position of Technical Marketing Engineer, initially on the Precision RTL synthesis product for 6 years and later on Catapult for 5 years. He has held various engineering and application engineering roles ASIC and FPGA RTL hardware design and verification. Stuart graduated from Brunel University, London, with a Bachelors of Science.

Content by Stuart Clubb

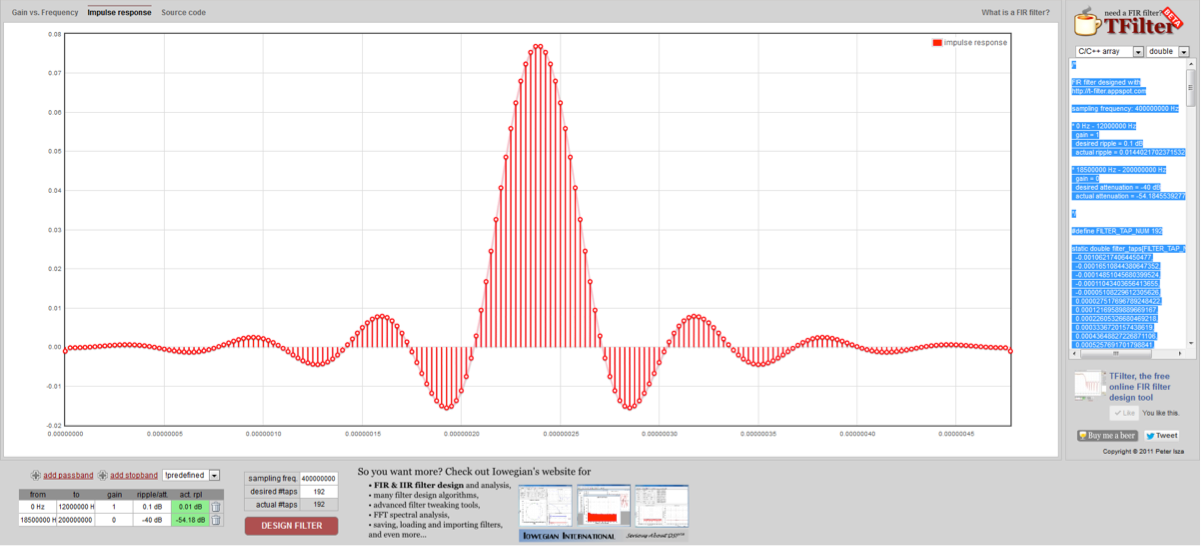

Filters

-

Modeling and Synthesizing Large Ratio Rate Adapters Reference Design

Arithmetic Functions Oct 13, 2013 Stuart Clubb Design Kit